Samsung เปิดตัวกระบวนการผลิตชิป 3nm ใช้เทคนิค GAAFET ประหยัดแบตขึ้น 50%

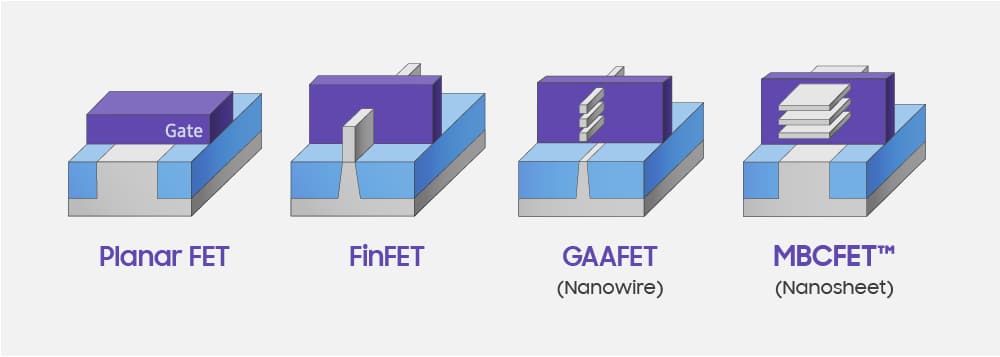

ล่าสุด Samsung Electronics ได้ออกมาประกาศผลิตชิปประมวลผลระดับ 3 นาโนเมตรใหม่แล้ว โดยใช้เทคโนโลยี Gate-All-Around (GAA) หรือ GAAFET แทนการใช้เทคโนโลยี FinFET ที่ใช้กันอยู่ในปัจจุบัน

โดยทั่วไปสำหรับเทคนิค GAA จะใช้การวาง Channel เป็นแบบ nanowire ที่มีขนาดเล็ก ทำให้กระแสไฟผ่านได้น้อย แต่ซัมซุงได้คิดวิธีแบบใหม่ที่เรียกว่า MBCFET™ (Multi-Bridge Channel Field Effect Transistor) ซึ่งจะเปลี่ยนการวาง Channel เป็นแบบ nanosheet ทำให้กระแสไฟผ่านได้มากขึ้น

เมื่อเปรียบเทียบประสิทธิภาพชิประดับ 7 นาโนเมตร ที่ใช้กันอยู่ในปัจจุบัน กับชิปที่ใช้เทคนิคใหม่ของซัมซุง พบว่าเทคนิคใหม่นี้ สามารถทำให้ขนาดชิปเล็กลงได้ 45%, ใช้พลังงานน้อยลง 50% และมีประสิทธิภาพเพิ่มขึ้นถึง 35% เพื่อนำไปใช้กับสมาร์ทโฟน รถยนต์ และตอบสนองอุปกรณ์ในยุค Artificial Intelligence (AI) และ IoT

อย่างไรก็ตามซัมซุงยังไม่ได้ออกมาระบุว่าชิป 3 นาโนเมตรจะเริ่มมีการผลิตจริงเมื่อใด แต่ตอนนี้ทางซัมซุงก็เริ่มปล่อยชิปดังกล่าวให้พาร์ทเนอร์ต่าง ๆ ได้ทดสอบแล้วเช่นกัน

สำหรับในช่วงสิ้นปี 2019 นี้ คาดว่าซัมซุงจะเริ่มผลิตชิป 6 นาโนเมตร และซัมซุงก็พัฒนาชิประดับ 4 นาโนเมตร ที่ยังใช้เทคนิค FinFET เสร็จแล้วเช่นกัน ต้องมาคอยดูกันว่าซัมซุงจะปล่อยชิปด้วยเทคนิคใหม่นี้เมื่อใด